Soc-e在FPGA上为任务关键型应用量身定制的IEEE 1588感知以太网交换机

摘要

现代FPGA和可重配置平台的长期供应,灵活性和集成能力已使这些器件成为航空航天和国防市场上新型嵌入式设备的首选技术。同样,以太网技术与用于亚微秒定时同步的IEEE 1588标准的使用相结合,简化了这些系统之间的集成和互操作性。

此外,该领域的最新创新,例如标准确定性以太网(TSN)或高可用性标准化协议(HSR / PRP),正在促进整个数据流的工程设计:精确的时间戳数据采集,实时流量通信和无缝与Edge计算和IT基础架构集成。

此外,FPGA供应商提供的图形设计工具套件也促进了这些完整系统的设计。这些工具与可配置的IP核心产品组合相结合,可以从高级角度无缝设计自定义的时间感知网络和数据采集设备。用于同步和联网的SoCe IP已被这些关键领域的公司广泛使用,以实现增值设备和嵌入式系统,这是经过实践检验的技术。本文介绍了这些方案中涉及的一些技术,并说明了IP和可重配置设备的好处。

关键词

以太网,IEEE 1588, TSN,IP,HSR / PRP,安全

1、精确时间协议-PTP

亚微秒同步在嵌入式系统中的需求越来越大。纳秒范围内的跟踪时间对于协调同步系统之间的事件以及分布式体系结构上的时间戳记值非常有用。在其他应用程序中,雷达,视频处理,机电一体化操作,GPS精确定位和确定性网络行为都得益于此级别的准确性。以太网上的IEEE 1588(PTP)提供亚微秒范围的同步,而无需将GPS接收器连接到每个设备。此外,它是一种故障安全系统,能够管理冗余PTP主站并可以分布在冗余以太网(HSR,PRP等)中。PTP基于分组锁定环(PLL)方法。像任何有源同步电路一样,IEEE 1588时钟是采用闭环算法实现的伺服系统。这些计算的最终目的是在所有同步设备中提供一个准确的64位定时器。 该计时器可用于数据时间戳记,分布式控制,甚至用于操作系统同步。

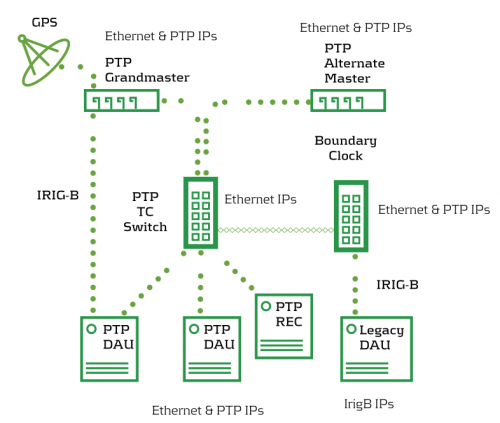

在典型的PTP网络中,涉及的元素是一个或多个PTP主时钟设备以及与该主设备同步和同步的PTP从设备。网络中的所有交换机均应支持PTP透明时钟操作,以更正所交换的PTP帧,以免丢失预期的精度。可以使用分隔不同时钟区域的PTP边界时钟设备以及能够用作主设备和从设备的PTP普通时钟来完成设置。图1总结了完整的PTP设置,包括数据采集单元(DAU),记录单元(REC)以及与许多航空航天系统中使用的传统Irig-B同步方案的潜在桥梁和网关。该图完成了适用于每个用例的同步IP。

2、以太网

以太网是一种众所周知的技术,有助于标准化分布式嵌入式系统之间的通信。在这些项目中,基本的以太网第2层操作员通过VLAN支持(标记,基于端口的路由等),IEEE 1588,专用MAC地址和QoS管理,基于硬件的数据预处理等得到了补充。与可定制的HDL IP内核的结合克服了以太网ASSP设备的局限性,并确保了许多这些关键任务项目中所需的源代码可访问性和长期供应。但是,该行业中定义的新项目要求克服标准以太网的局限性:缺少对已发送帧的确认,这可能会影响系统的可靠性以及无法处理实时流量。

3、高可用性以太网

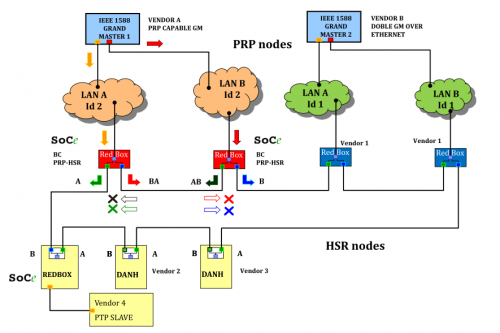

从这个意义上讲,高可用性无缝冗余(HSR)协议和并行冗余协议(PRP)提供了零延迟恢复时间,并且在以太网上不会丢失任何帧。HSR面向以太网环型拓扑,而PRP可以与两个独立的传统以太网络一起工作。实际上,可以将PRP,HSR和PTP结合使用,以从其特定功能中受益。图2表示SoCe和其他供应商在ISPCS 1588-plugfest中于2015年构建的网络拓扑,该网络拓扑支持PTP over PRP和HSR网络。

4、确定性以太网和TSN

确定性以太网允许以尽力而为的方式(常规以太网流量)合并在相同的媒体和网络实时流量中。为了简化不同供应商之间的互操作性,有一项强大的IEEE计划得到了思科,英特尔博通,赛灵思或博世等工业公司的支持。它被称为时间敏感网络—TSN。这是负责数据链路层标准的IEEE 802.1任务组的名称。该小组提供的规范将允许通过IEEE 802网络进行时间同步,低延迟的流服务。 TSN的独特之处在于其流以保证的带宽和确定的延迟交付。

5、IP和可重新配置设备

传统以太网,高可用性以太网,确定性以太网和精确定时技术在该行业的项目中多次组合。在诸如Radar之类的密集型DSP应用中,从PTP同步和使用以太网进行通信中受益是很有意义的。高端FPGA中高速数据采集,处理和通信的完全集成简化了产品的整个生命周期:从设计到维护。

可通过高级设计工具进行配置的,经过现场验证的IP核产品组合可以成为这些项目中的宝贵合作伙伴。 SoCe自2010年以来一直提供这些IP。主要的技术差异总结如下:

5.1 低延迟和无阻塞交换矩阵

关键任务设备的以太网交换机要求低延迟的交换时间,并要求ASSP以太网交换机设备提供更高的可靠性。标准以太网通信无法确保帧的传递,即使那些优先级最高的帧也是如此。它依赖于网络设计人员的任务,即正确地设计所有涉及的元素。首要要求是确保设备中嵌入的开关矩阵的低延迟。对于MES IP测得的等待时间大约是64字节帧,这将这种实现定义为一种真正的低等待时间。

结合这种低延迟操作,需要一种能够消除不希望出现的行头(HOL)效应的架构,该效应限制了交换机的有效性能。如果矩阵在其输出端口中遇到争用或拥塞问题,则此效果会阻止将传入数据包传递到端口目标。

在FPGA上实现的以太网交换机可以满足所有这些要求,同时,FPGA供应商确保为实施中选择的可重配置设备提供长期供应。从这个意义上讲,经过现场验证的HDL编码IP的可用性为航天和国防领域的嵌入式项目提供了安全可靠的解决方案。SoC-e交换IP基于优化的无阻塞交换矩阵,该矩阵与每个端口的分布式内存相结合,可管理1GbE流量的100%带宽,从而确保了多达16个端口的交换矩阵中的非HOL效应。根据实现的功能(端口数量,功能等)和FPGA资源,该代码提供了20多个通用参数,这些参数可以在合成时选择,以获得最优化的解决方案。

5.2 IEEE 1588支持

对于以太网连接的设备而言,获得GPS范围定时同步的好处是该行业的明显优势。但是,工程IEEE 1588系统并不简单。

即使对于简单的IEEE 1588设置,也必须为网络提供主时钟设备以及与主时钟同步的从时钟。此外,所有交换机都应能够纠正IEEE 1588帧。透明时钟设备支持此操作,并校正交换机的停留时间和与相邻端口之间的部分关联的链路延迟。在FPGA上实现的以太网交换机通过硬件管理此透明时钟操作,从而简化了IEEE 1588功能的集成。SoC-e交换IP对每个端口都独立支持此功能,即使是紧凑的对等操作模式也可以自动计算并应用链路延迟补偿。如果节点需要支持“主”或“从”操作模式,则SoCe IP和软件产品组合将完成所需的交钥匙解决方案,以满足设备的同步需求。

5.3 无缝集成和配置以实现最佳实施

基于现代FPGA的设计的高密度允许在单个设备中集成强大的功能。通常在单个设备中结合使用数据采集,数字信号处理和网络模块。此外,得益于Xilinx Zynq MPSoC Ultrascale +之类的新型混合可重配置平台,可以将功能强大的多处理器体系结构嵌入高端可重配置逻辑中。

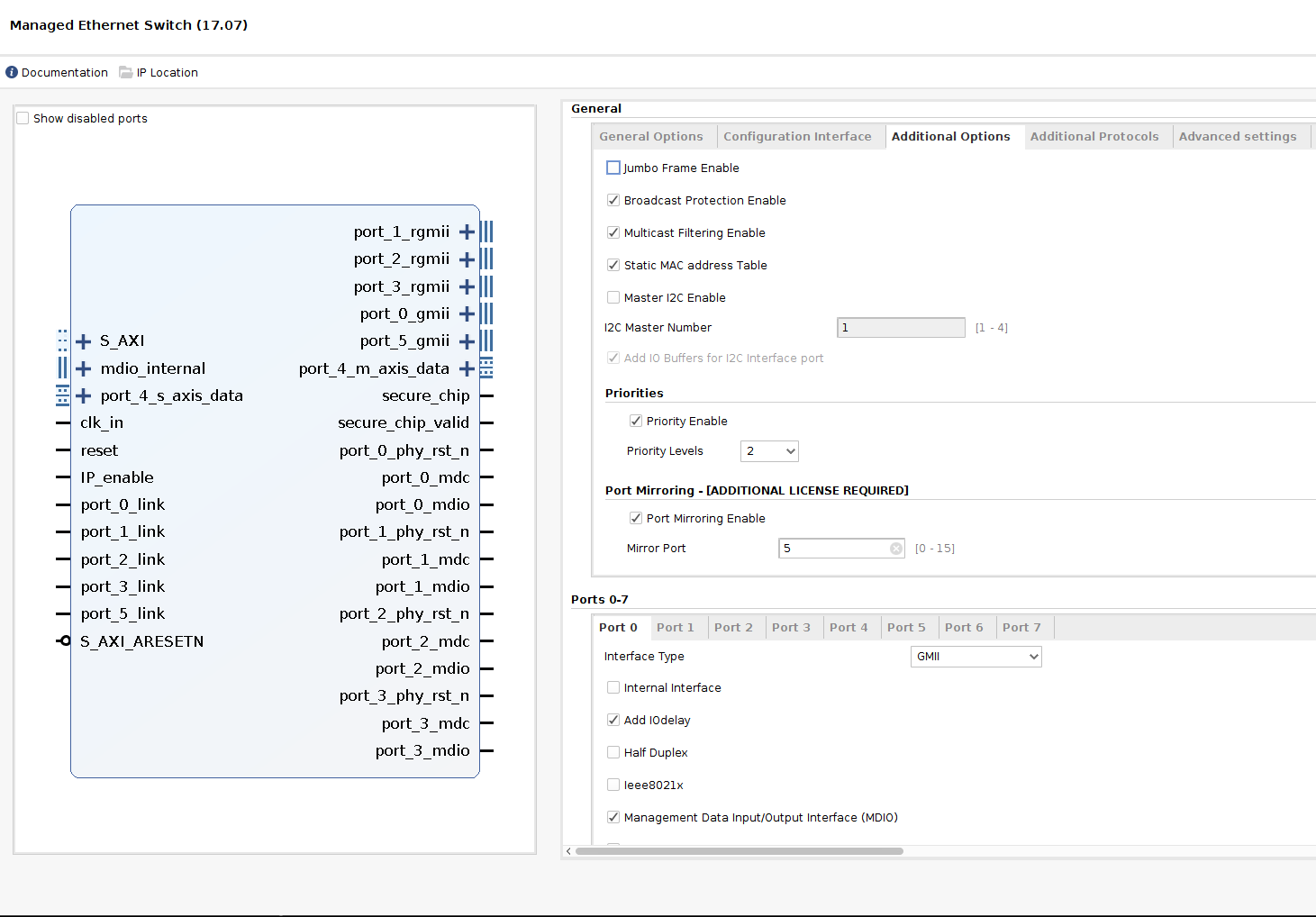

幸运的是,设计方法正在不断发展,如今,从高级设计图形工具来面对这些设计是可行的。这些新一代工具的一个很好的例子是Vivado Design Suite。该工具为FPGA设计提供了图形化的高级入口点。如果使用第三方专用IP内核可以提供所需的功能,则设计人员仅需使用用户友好的菜单为IP选择所需的配置参数,该工具最终将为FPGA生成配置文件。因此,不需要在HDL级别上工作。

例如,图3显示了受管理的以太网交换机(MES)IP配置参数的一个屏幕快照,该屏幕快照总结了与具有广播保护,组播过滤,静态MAC表管理,优先级和内部端口镜像聚合的其他选项相关的泛型。此外,该IP具有等效的配置菜单,用于选择配置接口,交换机支持的附加协议的实现,与每个PHY和端口的通信接口以及许多其他接口。这种模块化是将不同IP组合以生成量身定制的网络设备的宝贵功能。

5.4 FPGA上的IEEE 1588自定义开关

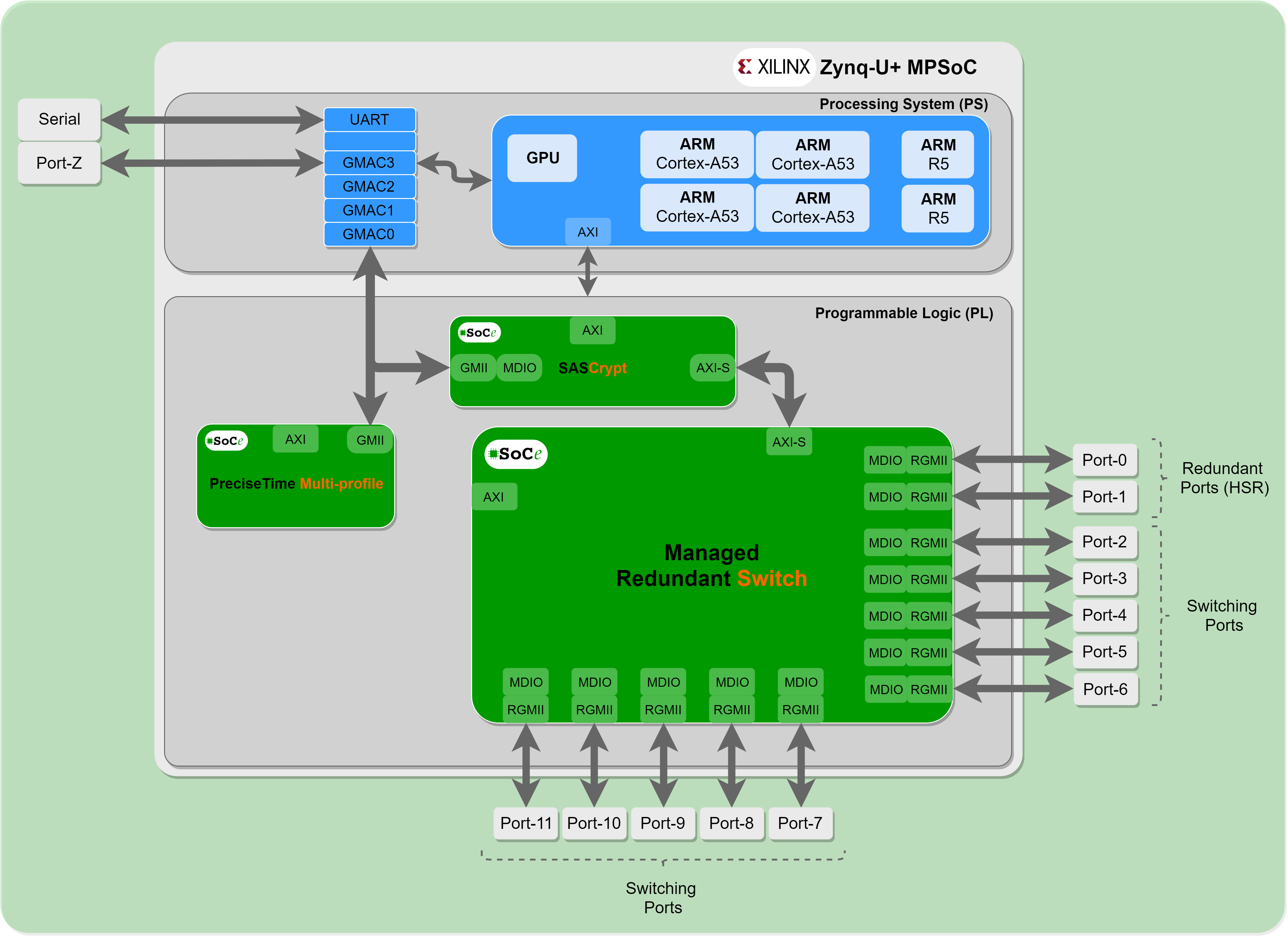

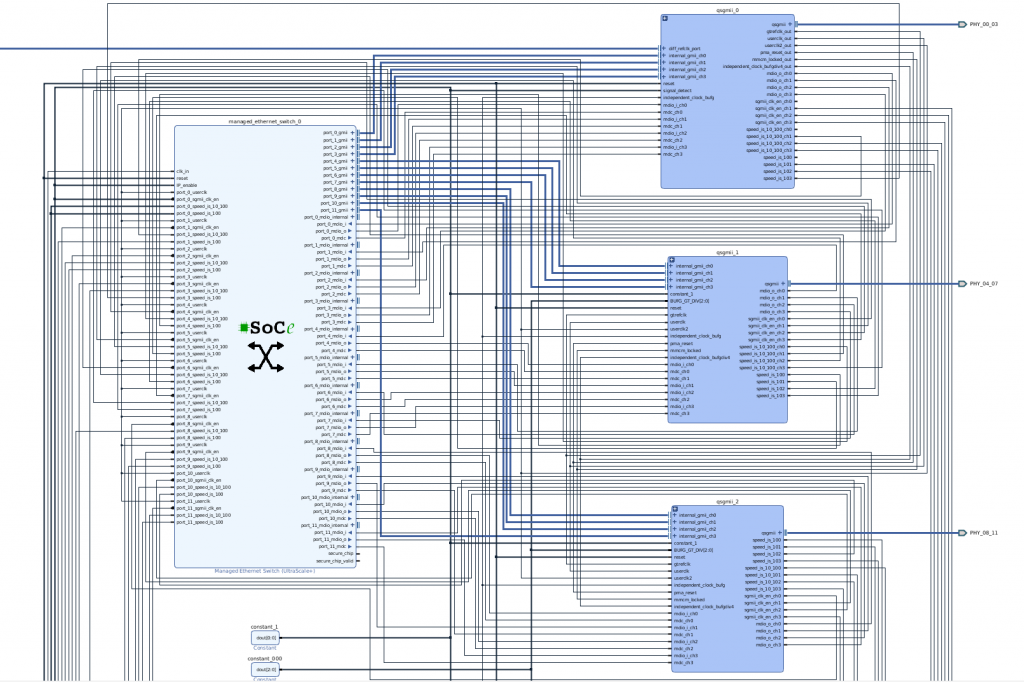

为了说明这种模块化,图4所示的框图表示可重配置平台上支持IEEE 1588的复杂交换机的框图。

该设计总共具有10个千兆以太网(GbE)和2个HSR / PRP / GbE以太网端口。目标设备是Xilinx Zynq MPSoC Ultrascale +,其在ASIC部分中包括处理系统(PS),4个ARM CorteX-A53 CPU,2个ARM-R5 CPU,1个ARM Mali GPU),内存控制器和连接性外围设备。在称为可编程逻辑(PL)的可重新配置部分中,该平台嵌入了一个大型FPGA。在此示例中,PL中实现的功能包括低延迟联网,亚微秒精度计时和实时流量的专门安全性。

这些交换模块支持透明时钟功能。此外,由于精确时间多配置文件(PTM)IP内核与PTP软件堆栈结合运行,因此该系统具有IEEE 1588主,从和边界时钟功能。

在这种设计中,在PL部分中实现的嵌入式交换机体系结构使用固定部分中可用的一个GMAC与PS部分进行通信。这样,CPU中运行的软件和操作系统对网络体系结构的访问是透明的。值得一提的是,在此GMAC与交换基础架构之间的链接中,如何包含专用的线速加密模块。它是SAScrypt IP的一个实例。该IP负责对具有严格实时要求的以太网类型的通信进行加密和解密。

图5详细说明了Vivado高级设计,该设计使用MRS IP实现了12个千兆以太网端口。该配置使用3个Xilinx QSGMII模块完成,该模块用于直接驱动嵌入到该项目目标设备中的Multi-Gigabit收发器(MGT)。

5.5 减少风险和开发时间

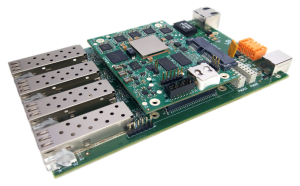

自定义开关项目获得的经验表明,如果有经过现场验 证的参考平台,则开发工作将大大减少。通常需要花费大量的工程时间来寻找以太网PHY的正确配置或寻找动态内存控制器的有效参数。为了简化这些任务,SoCe开发了坚固的模块上系统(SoM)和载体,可用于开发和试验阶段,甚至可直接集成到设备中。这些模块的产品组合仅包括FPGA,Zynq和Zynq Ultrascale + MPSoC板。从连接性的角度来看,这些模块是兼容的,从而可以进一步升级系统。这些SoM的一个示例是图6中所示的SMARTmpsoc模块。它已插入SMART载板上。这款紧凑的主板尺寸为88*66mm,包括Xilinx Zynq MPSoC Ultrascale + XCZU3EG器件,2 GB DDR4 RAM存储器,64 MB Quad SPI闪存,16GB eMCC闪存,5x以太网Phys 10/100 / 1000BaseT-X,3x PS-GTR收发器支持其他高速连接通道,例如SGMII,实时时钟电池(RTC),安全IC(TPM,陀螺仪等)和SATA-3磁盘接口连接器。

该SoM可以插入可用的一种载体中,例如图6中所示的Brick,也可以插入客户板上。该模块的典型应用是高级以太网网络,结合了边缘计算和网络安全

6、结论

新的同步和网络技术与可重新配置的设备相结合,正在简化用于航空航天和国防系统的复杂系统的设计和维护。本文介绍的用例说明了经过现场验证的IP如何允许灵活的组合来获得量身定制的FPGA实施方案,这些方案能够将纳秒范围的同步与高可用性网络和线速安全性集成在一起。这些技术是这些先进行业需求的关键驱动力。